Connect FTDI SPI with ICE40 FPGA

The open source toolchain for ICE40 FPGA works exceptionally well. For example, APIO (link) combines synthesis, simulation and programmer into one easy-to-use CLI, which makes ICE40 FPGAs fun to play with, in strong contrast to bulky, snail-slow Xilinx FPGA toolchains.

1. FTDI SPI Bitstream to Flash Chip

Because of the free ICE40 open source toolchain, many low-price development board has spun up around ICE40 FPGAs. Most of them use FTDI FT232H in SPI mode to write bitstream to a Flash chip, which then in turn configures the ICE40 FPGA.

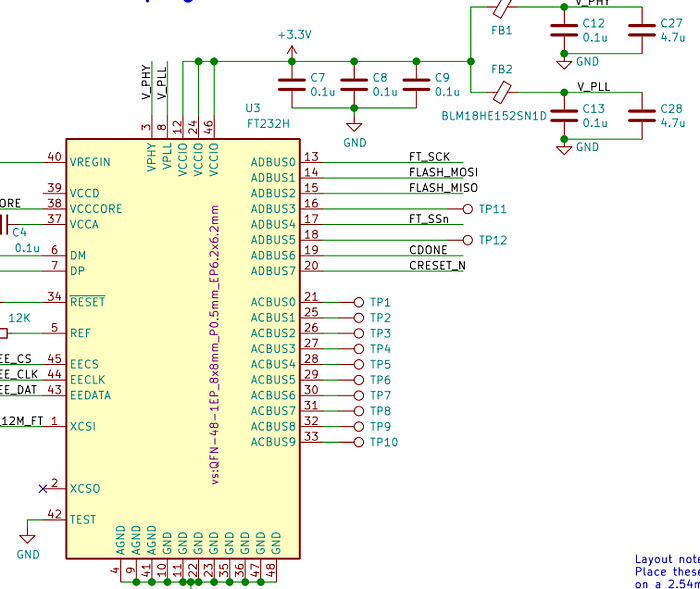

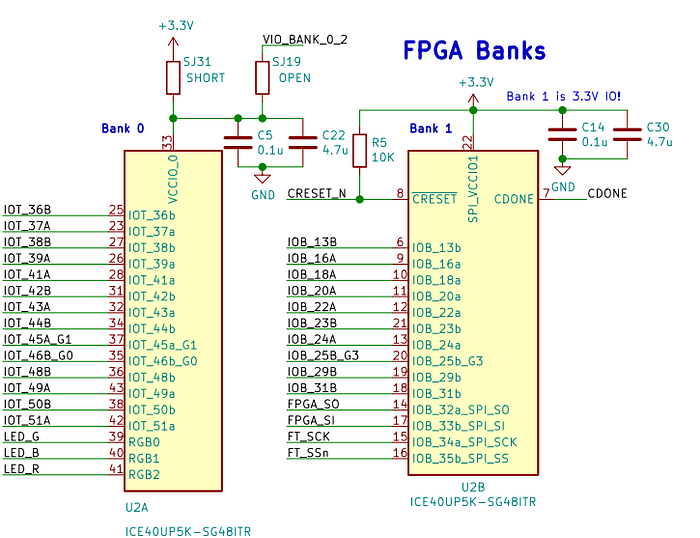

For example, in Upduino 3.1 schematic

FT232H has its SPI signals going into the Flash chip to send ICE40 bitstream. The bitstream is then read into ICE40 via its SPI lines (see schematic snippets below) for configuration upon FPGA power up.

In this case, the Flash chip serves as a SPI slave, whereas both FTDI and ICE40 serve as SPI masters.